Typical gate array platforms use dedicated areas called channels, for inter-cell routing between rows or columns of MOS transistors. The figure given below shows the basic processing steps for gate array implementation. The patterning of metallic interconnects is done at the end of the chip fabrication process, so that the turn-around time can still be short, a few days to a few weeks. These uncommitted chips can be stored for later customization, which is completed by defining the metal interconnects between the transistors of the array.

The first phase results in an array of uncommitted transistors on each GA chip. Gate array implementation requires a two-step manufacturing process. While user programming is important to the design implementation of the FPGA chip, metal mask design and processing is used for GA. The gate array (GA) ranks second after the FPGA, in terms of fast prototyping capability.

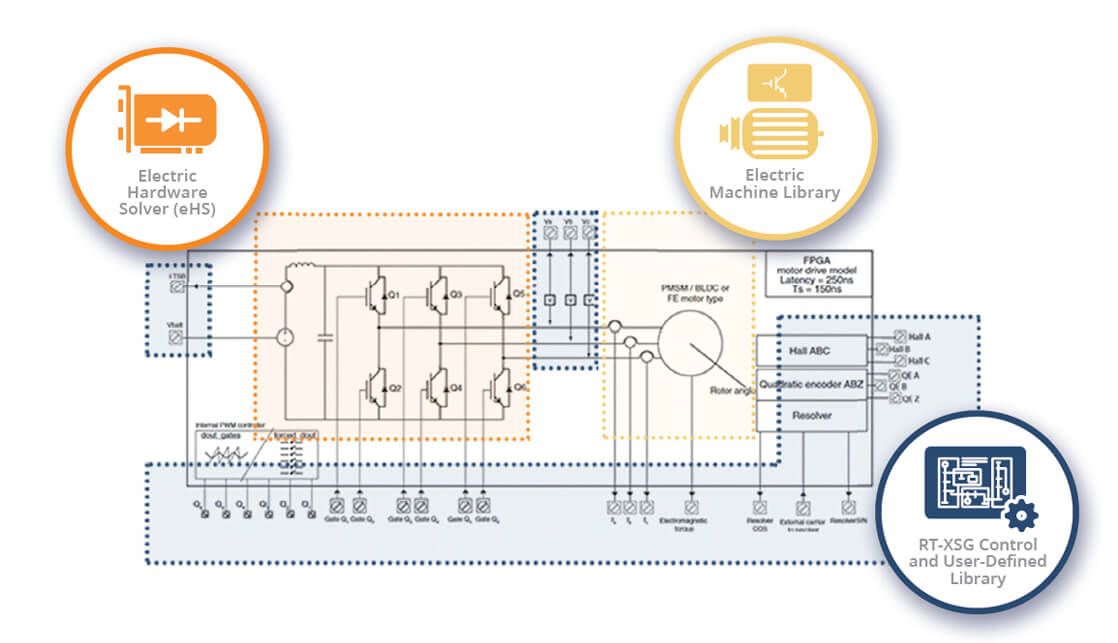

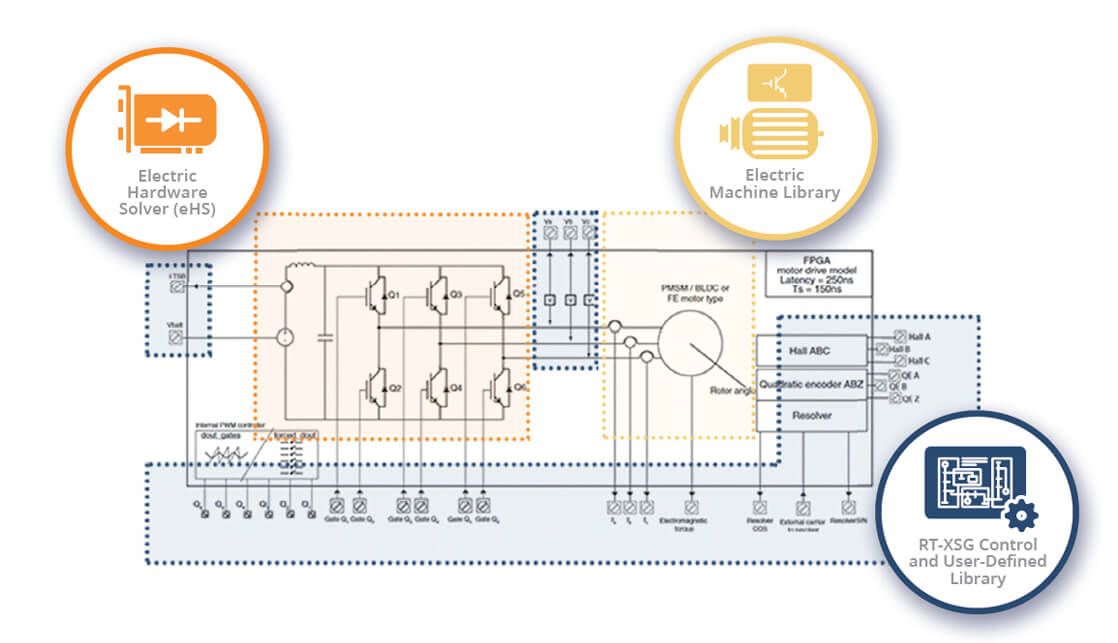

The only disadvantage is, it is costly than other styles. No physical manufacturing steps are involved in it. It requires very small time starting from design process to functional chip. After programming, CLB and PSM are placed on chip and connected with each other with routing channels. The functionality of CLB’s and PSM are designed by VHDL or any other hardware descriptive language. The number of CLB it contains only decides the complexity of FPGA. The inter connection between CLB and I/O blocks are made with the help of horizontal routing channels, vertical routing channels and PSM (Programmable Multiplexers). For each module of logic level composition, there are CLB’s (Configurable Logic Blocks).ĬLB performs the logic operation given to the module. There are I/O blocks, which are designed and numbered according to function. A typical model FPGA chip is shown in the given figure. Programmable interconnections are available for users or designers to perform given functions easily. It contains ten thousand to more than a million logic gates with programmable interconnection. #FPGA SIMULATION A COMPLETE STEP BY STEP GUIDE PDF FULL#

The full form of FPGA is “ Field Programmable Gate Array”.

0 kommentar(er)

0 kommentar(er)